Table of Contents >> Show >> Hide

- What Is the OpenISA VEGAboard, Really?

- Why the “Free” Part Mattered So Much

- Key VEGAboard Features That Made It More Than Hype

- OpenISA Was Selling an Ecosystem, Not Just a Board

- Software Support Helped the VEGAboard Punch Above Its Weight

- Why RISC-V Needed a Board Like This

- What Made the Launch Newsworthy

- Was the VEGAboard a Big Industry Turning Point?

- Who Should Care About the VEGAboard Story Today?

- Final Thoughts

- Experience and Practical Takeaways From the VEGAboard Story

- SEO Tags

Every so often, the embedded world gets a product launch that feels less like a press release and more like a dare. OpenISA’s VEGAboard was exactly that kind of moment. Instead of quietly dropping another developer board into an already crowded drawer of blinking hardware, OpenISA came out swinging with a simple pitch: here is a RISC-V development board, here is a growing open ecosystem around it, and yes, a limited number of boards are available free in the United States.

That is the kind of sentence that makes engineers sit up straight, hobbyists open too many browser tabs, and procurement teams suddenly pretend they have never heard the word “budget.” But the real story behind the OpenISA VEGAboard was never just the price tag. The bigger story was what the board represented: a practical, low-power, developer-friendly way to get hands-on with RISC-V while also tapping into real tools, real operating systems, and a real community.

In other words, the OpenISA VEGAboard was not trying to be a science fair prop. It was trying to help push RISC-V from fascinating idea to usable platform.

What Is the OpenISA VEGAboard, Really?

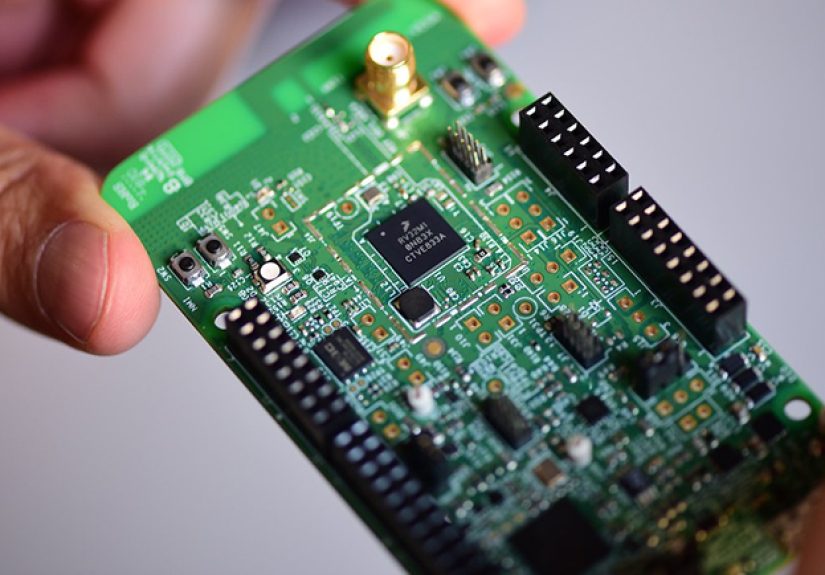

At first glance, the VEGAboard looks like a compact embedded development board with familiar maker-friendly DNA. It includes Arduino-compatible headers, onboard sensors, flash storage, an RGB LED, push buttons, and wireless capabilities. So far, so normal. But underneath that friendly surface is the part that makes embedded developers lean in a little closer.

The board is built around NXP’s RV32M1, a multicore SoC that mixes two Arm cores and two RISC-V cores on one platform. That hybrid setup is what gave the VEGAboard its identity. Instead of treating RISC-V like a lab experiment floating in isolation, OpenISA packaged it into a board that could help developers compare architectures, explore software portability, and prototype embedded applications with fewer excuses and fewer roadblocks.

The RISC-V side features the RI5CY and ZERO-RISCY cores derived from the PULP platform, while the broader SoC also includes Cortex-M4 and Cortex-M0+ cores. That means the VEGAboard was never just shouting, “Look, RISC-V!” It was saying something far more useful: “Here is a realistic development environment where RISC-V can live next to established embedded architectures and prove its value.”

Why the “Free” Part Mattered So Much

Let’s be honest: “free developer board” is the kind of phrase that can make grown engineers behave like people sprinting toward a clearance bin on Black Friday. But the OpenISA giveaway strategy was more thoughtful than simple promotional bait.

By offering a limited number of VEGAboards free of charge, OpenISA lowered the usual barriers that slow platform adoption. Engineers did not have to spend weeks convincing managers that a new ISA was worth exploring. Students and academics did not need a deep hardware budget. Makers and early adopters did not have to gamble on unfamiliar silicon just to satisfy curiosity. OpenISA effectively said, “Stop theorizing. Build something.”

That matters because platform adoption almost never happens through white papers alone. It happens when developers can compile code, flash firmware, break things, fix them, and tell their friends what worked. The free-board move encouraged exactly that kind of grassroots experimentation. It was smart, practical, and a little sneaky in the best possible way.

Key VEGAboard Features That Made It More Than Hype

A mixed-core design with actual teaching value

The RV32M1 architecture made the VEGAboard especially interesting because it let developers see how RISC-V could fit into a broader embedded design strategy. This was not a lonely single-core novelty board asking to be graded on a curve. It was a platform with multiple cores, multiple roles, and room for serious exploration.

That made it useful for architecture evaluation, RTOS experiments, wireless prototyping, and teaching environments. Developers could work with the RISC-V cores directly while also understanding how a heterogeneous embedded system behaves in the real world. For students and embedded teams alike, that is far more valuable than a board that only exists to print “Hello, world” and retire with dignity.

Wireless and sensor support for real embedded projects

The VEGAboard also shipped with the kind of onboard hardware that makes a development platform feel immediately useful: integrated wireless support, external SPI flash, sensors, microSD capability, RGB LED feedback, push buttons, and expansion headers. In practice, that meant developers could build proof-of-concept applications without turning their desk into a suspicious-looking pile of breakout boards and tangled jumper wires.

Wireless support was especially important. RISC-V conversations often drift into abstraction, standards politics, or long-term industry strategy. The VEGAboard pulled those conversations back toward actual embedded use cases: connected devices, sensor-driven applications, low-power IoT prototypes, and edge firmware development.

Arduino-style accessibility without dumbing things down

One of the VEGAboard’s quiet strengths was accessibility. Arduino-compatible expansion headers made the board approachable for developers coming from maker ecosystems, while the board’s multicore design and toolchain support gave serious engineers enough depth to do meaningful work. That balance matters. A platform grows faster when beginners can start with it and professionals can keep using it after the novelty wears off.

OpenISA Was Selling an Ecosystem, Not Just a Board

The smartest thing about the VEGAboard launch may have been that OpenISA did not frame the board as a standalone miracle object. It framed it as an entry point into an ecosystem.

That distinction matters because hardware alone rarely wins. Developers care about SDKs, documentation, debuggers, RTOS support, middleware, examples, forums, and whether they can still find help after the launch buzz fades. OpenISA understood that and built the VEGAboard story around software, tools, and community.

The launch was backed by partners and ecosystem contributors including PULP Platform, Express Logic, Foundries.io, Ashling, IAR Systems, and SEGGER. That support gave the board credibility. Suddenly this was not just “a cool RISC-V board.” It was a board with surrounding infrastructure, familiar tools, and a path toward serious experimentation.

That is also why the OpenISA website itself mattered. It acted as a hub for downloads, community discussion, documentation, and getting-started materials. In a market where developer experiences are often ruined by scattered downloads and broken forum links from 2017, a central hub was more than convenient. It was strategic.

Software Support Helped the VEGAboard Punch Above Its Weight

A development board lives or dies by software support. Beautiful hardware with weak tooling is basically a very expensive coaster. The VEGAboard avoided that trap by landing in ecosystems developers already respected.

Zephyr support gave the board an open-source RTOS story that aligned neatly with the broader RISC-V vision. FreeRTOS support made the board relevant to mainstream embedded developers who wanted something familiar, proven, and practical. NuttX documentation later reinforced that the board had ongoing value in open embedded communities. And OpenISA’s own GitHub release materials provided SDK installers, documentation, and toolchain packages for Windows, Linux, and Mac.

That is the kind of support stack that turns curiosity into momentum. It also helped answer the most important question every engineer silently asks when evaluating new hardware: “Can I actually get real work done on this thing?”

With the VEGAboard, the answer was much closer to “yes” than many early-stage open hardware launches ever manage.

Why RISC-V Needed a Board Like This

RISC-V has always had a strong conceptual pitch. It is open, flexible, and royalty-free at the ISA level, which gives companies and developers more control over how they build and customize silicon. That sounds great in conference talks, investor decks, and opinion articles written by people who enjoy saying “ecosystem” before coffee.

But concepts do not build market trust. Working boards do.

The VEGAboard helped make RISC-V feel tangible. It gave developers a place to test assumptions, compare behavior, port software, evaluate tools, and learn by doing. And that hands-on element is crucial, because RISC-V’s long-term success depends not only on chip announcements but on the boring, beautiful mechanics of everyday development: debugging, firmware flashing, board bring-up, driver support, RTOS integration, and community knowledge-sharing.

In that sense, the VEGAboard launch did something bigger than introduce hardware. It reduced friction. And in technology, reducing friction is often how revolutions sneak in through the side door.

What Made the Launch Newsworthy

Several things made the OpenISA VEGAboard launch stand out.

First, it offered a real board instead of yet another promise about what RISC-V might become someday. Second, it tied hardware to a broader open-development strategy instead of treating the board like a one-off gadget. Third, the mixed-core RV32M1 design made the board genuinely distinctive in a market full of simpler single-architecture platforms. And fourth, the limited free-board program was a sharp adoption play that invited developers to join the experiment rather than merely applaud from the sidelines.

That combination made the VEGAboard launch more than a headline. It made it a useful case study in how open hardware ecosystems grow: not just with standards, but with boards, software, documentation, and enough generosity to get devices into developers’ hands.

Was the VEGAboard a Big Industry Turning Point?

Not by itself. No single development board flips an industry overnight, and anyone who claims otherwise probably also owns a collection of “disruptive” buzzwords in a climate-controlled display case.

What the VEGAboard did do was help legitimize a stage of the RISC-V journey. It showed that the conversation had moved beyond theory and into practical enablement. It demonstrated that open ISA advocacy could be paired with real hardware, real tools, and real developer workflows. It also highlighted how important collaboration is in the embedded world. A board is stronger when the RTOS people, debugger people, toolchain people, and silicon people all show up to the same party.

So no, the VEGAboard was not the entire story of RISC-V. But it was a meaningful chapter, and one that helped make the ecosystem feel more usable, more visible, and more inviting.

Who Should Care About the VEGAboard Story Today?

Embedded developers should care because the VEGAboard showed how open architecture adoption actually happens in practice. Students and educators should care because it demonstrated the educational power of mixed-core, hands-on platforms. Hardware strategists should care because it revealed the value of lowering adoption barriers at the right moment. And anyone tracking the evolution of RISC-V should care because the VEGAboard helped bridge the gap between technical idealism and practical engineering work.

Even if you never touch this specific board, the lesson still holds: open architectures win more mindshare when they arrive with boards you can test, software you can run, and documentation that does not feel like a punishment.

Final Thoughts

OpenISA’s free RISC-V VEGAboard launch was clever for all the right reasons. It offered a developer board, yes, but more importantly it offered a doorway. The board’s mixed-core RV32M1 design, wireless features, sensor set, expansion options, and software support made it practical. The OpenISA ecosystem, partner backing, and giveaway strategy made it inviting. Put those together, and the VEGAboard became more than launch-day noise. It became a hands-on argument for why RISC-V deserved serious attention.

And maybe that is the most interesting part. The VEGAboard did not try to win with chest-thumping marketing or vague future promises. It won by giving developers something concrete to test, tweak, and trust. In embedded systems, that kind of honesty goes a long way.

Experience and Practical Takeaways From the VEGAboard Story

What makes the OpenISA VEGAboard memorable is not only the specification sheet, but the kind of experience it represents for developers. A board like this tends to create a very specific emotional arc. At first there is curiosity: “A free RISC-V board? Sure, I’ll click that.” Then there is skepticism: “Okay, but will this turn into three days of driver pain and a fourth day of questioning my career choices?” Then, if the platform is decent, curiosity turns into momentum.

The VEGAboard seemed designed to speed up that momentum. The hardware gave developers enough built-in features to start experimenting without building a support tower of external modules. The OpenSDA and debug path reduced the chance that bring-up would feel like a treasure hunt. The availability of SDK materials and toolchains meant developers could move from announcement to setup without the usual ritual of hunting dead links across abandoned forums. That is not glamorous, but it is exactly what shapes the real experience of a board.

There is also a strong educational experience baked into the VEGAboard idea. If you are a student, instructor, or self-taught embedded developer, a mixed-core board is a terrific way to understand architecture choices in a practical setting. You are not just reading about RISC-V as an abstract open standard. You are seeing how it coexists with established Arm cores, how RTOS support lands on actual silicon, and how embedded platforms are built as systems rather than as isolated processor diagrams.

For hobbyists, the VEGAboard experience likely felt like getting access to a slightly more serious toy box. You could play, but you could also learn something meaningful. For professionals, the board’s value was different. It provided a low-risk way to evaluate whether RISC-V deserved engineering attention inside future products, internal tools, or training efforts. That is a much bigger deal than a giveaway gimmick. Cheap evaluation lowers organizational resistance. Free evaluation lowers it even more.

There is another lesson here for anyone launching developer hardware today: do not just ship silicon, ship confidence. Confidence comes from documentation, examples, community structure, and a setup path that does not make new users feel unwelcome. OpenISA understood that well enough to make the VEGAboard story stick. The board had enough features to be useful, enough openness to be exciting, and enough ecosystem support to feel legitimate.

So the experience lesson is simple. Developers do not fall in love with hardware because a company says the future is open. They fall in love when the board boots, the tools behave, the docs make sense, and the first successful demo happens before dinner. The OpenISA VEGAboard mattered because it gave RISC-V one more chance to create exactly that kind of first impression.